The open source methods that have reshaped the software industry are now substantially transforming microprocessor technology development, licensing, and implementation. The OpenHW Group, a global, not-for-profit, member-driven organization headquartered in Ottawa, Canada, and partnered with the Eclipse Foundation, is a major driver of this shift. The OpenHW Group worldwide membership is developing the CORE-V family of open source, RISC-V microprocessor cores, along with associated accelerators, interfaces, enabling hardware and System on Chip (SoC) platforms, and software toolchains in a comprehensive ecosystem approach.

Starting from a single project in 2019, OpenHW Group now fosters over twenty open source projects, and the list grows by the month. In OpenHW Group’s model, industry, academic, and individual contributors drive innovation within a collaborative framework. Each participant helps to advance projects according to their priorities and skillsets, reducing development costs and fostering an ecosystem of stakeholders with a shared interest in bringing open source projects to fruition.

The output of an OpenHW processor core project is typically a set of open source Intellectual Property (IP) that includes fully verified Register Transfer Level (RTL) code, a user manual and test benches that together can be used as the heart of a semiconductor device design. OpenHW projects are developed under permissive open source licenses, such as Solderpad 2.0 (which builds on Apache 2.0), that provide implementers the freedom to innovate, to customize, and to commercialize. OpenHW’s use of the Eclipse Development Process (EDP) ensures that IP adopters have full confidence in the provenance of open source contributions and the integrity of project outputs.

The OpenHW Group’s vision of an industrial quality, open source processor core ecosystem has the potential to be a global industry game-changer.

The RISC-V ISA: a Platform for Innovation

The availability of the free and open RISC-V Instruction Set Architecture (ISA) has unleashed a new frontier of innovation in the processor design community. However, the RISC-V ISA specification covers just the ISA itself and does not provide tangible processor designs. That’s where the OpenHW Group comes in. OpenHW Group members design and verify RISC-V processor cores (the CORE-V family) to industrial quality levels and release the tested processor code as open source artifacts.

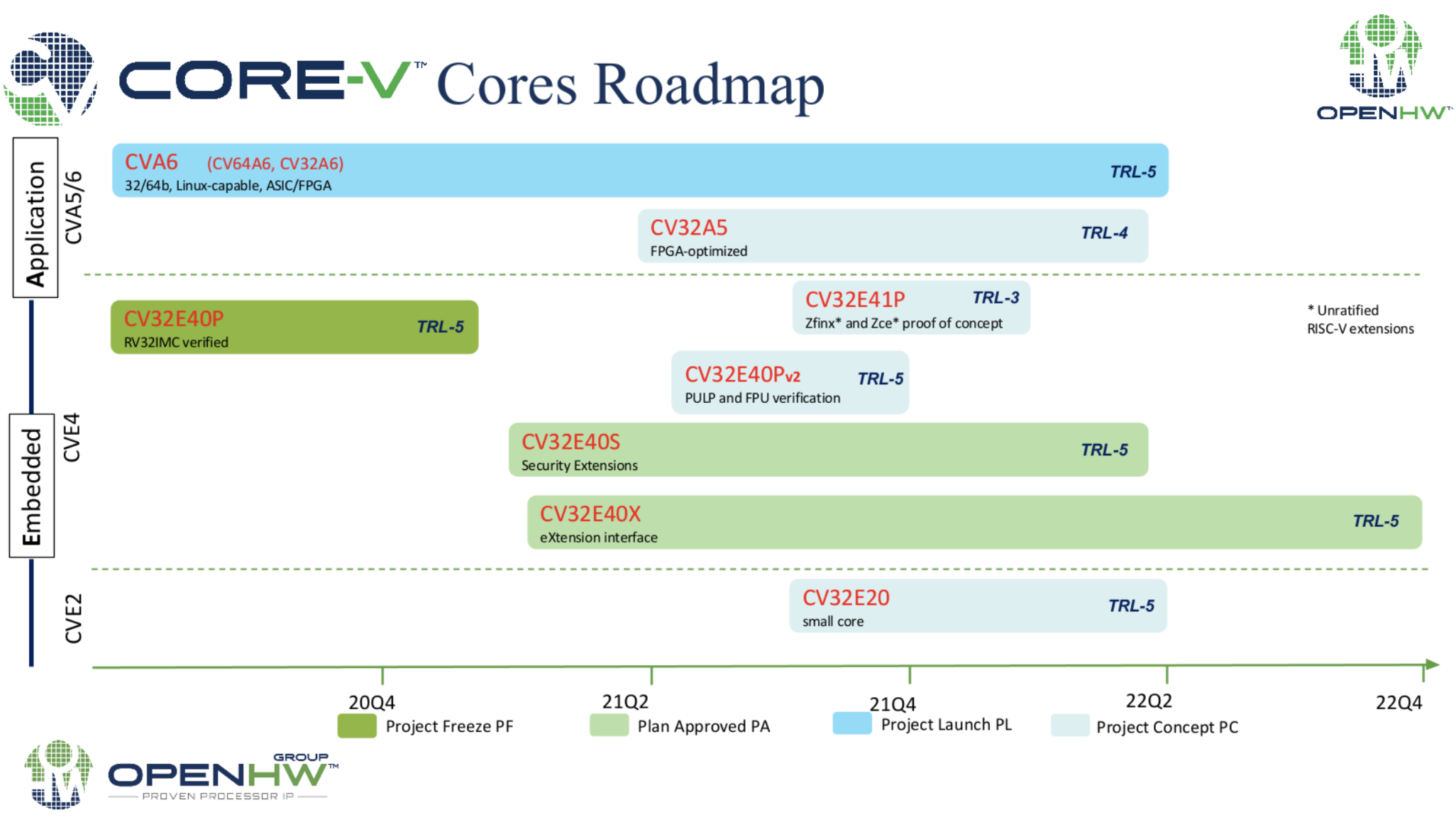

The OpenHW Group processor core designs are grouped under the Eclipse Foundation “CORE-V Cores” project. As shown in Figure 1, current CORE-V Cores projects include:

- The CVA6 family of 64/32 bit application processors intended for applications requiring higher performance and Linux support;

- The CVA5 family of high performance, FPGA-optimized application processors;

- The CVE4 family of 32 bit embedded-class cores intended for a variety of IoT and edge applications, typically running FreeRTOS, other real-time operating systems, or in bare-metal scenarios. Starting with the CV32E40P released in 2020, the family includes the CV32E40Pv2 integrating PULP extensions, the CV32E40X with extension interface, the CV32E40S security focussed core, and the CV32E41P with support for compressed instructions.

- The CVE2 microcontroller family, intended for example to replace state-machine logic in embedded devices with a small and power efficient processor.

Figure 1: CORE-V Cores Roadmap

Several of the CORE-V cores originated as RISC-V designs from leading universities - ETH Zurich, University of Bologna, and Simon Fraser University. What further ties them together is the OpenHW Group approach to industrial development practices, in which industry standard approaches and tools are used - including comprehensive documentation, rigorous design and verification practices and use of commercial EDA tools. In the OpenHW Group flow, we believe that using standard industry toolsets and methods is a prerequisite to achieving industry levels of quality in the open source artefacts produced. The verification environment (core-v-verif), implemented using System Verilog and the Universal Verification Methodology (UVM), is one of the most important open source artifacts produced by OpenHW Group.

Additional Projects Support the OpenHW Ecosystem

Many other projects are also required to support a vibrant OpenHW ecosystem. For example, the Software Task Group supports the CORE-V ecosystem with a full set of compiler, IDE, and board-level support projects (Table 2).

Table 2: Current OpenHW Software Task Group Projects

| Project | Description |

| CORE-V IDE-CDT | Eclipse IDE supporting CORE-V |

| CORE-V GNU GCC Tools | GNU Compiler Collection (GCC) tool chain supporting CORE-V |

| CORE-V LLVM Tools | LLVM tool chain supporting CORE-V |

| CORE-V FreeRTOS | FreeRTOS supporting CORE-V |

| CORE-V HAL | Hardware Abstraction Layer for CORE-V devices |

| CORE-V SDK | CORE-V Software Development Kit |

Similarly, our Hardware Task Group develops platform solutions to support the CORE-V processors (Table 3).

Table 3: Current OpenHW Hardware Task Group Projects

| Project | Description |

| CORE-V MCU | System-on-chip implementation of CV32E40P on GF22 |

| CORE-V MCU Verilator Model | Verilator model of MCU/CV32E40P for software development |

| CORE-V DEVKIT | Development kit including PCB-mounted CORE-V MCU |

OpenHW Group members are hard at work on a silicon implementation of our first released processor, the CV32E40P embedded-class core (E40P). The E40P has been integrated into the CORE-V MCU integrated circuit, which is currently available on FPGA based emulation platforms, and will be fabricated at Global Foundries using 22FDX process technology in 2022.

Eclipse Development Processes and OpenHW Group Approach to Project Management

As mentioned above, the OpenHW Group follows the Eclipse Foundation Development Process. Key elements of the process include:

- Contributor agreements including developers’ certificates of origin;

- Election of committers based on demonstrated technical and procedural merit;

- Vetting of contributions for compliance with the project’s open source licenses and intellectual property rules.

These, and the other aspects of the development process, ensure that OpenHW Group project artifacts are developed under one of the industry’s most comprehensive and rigorous open source frameworks.

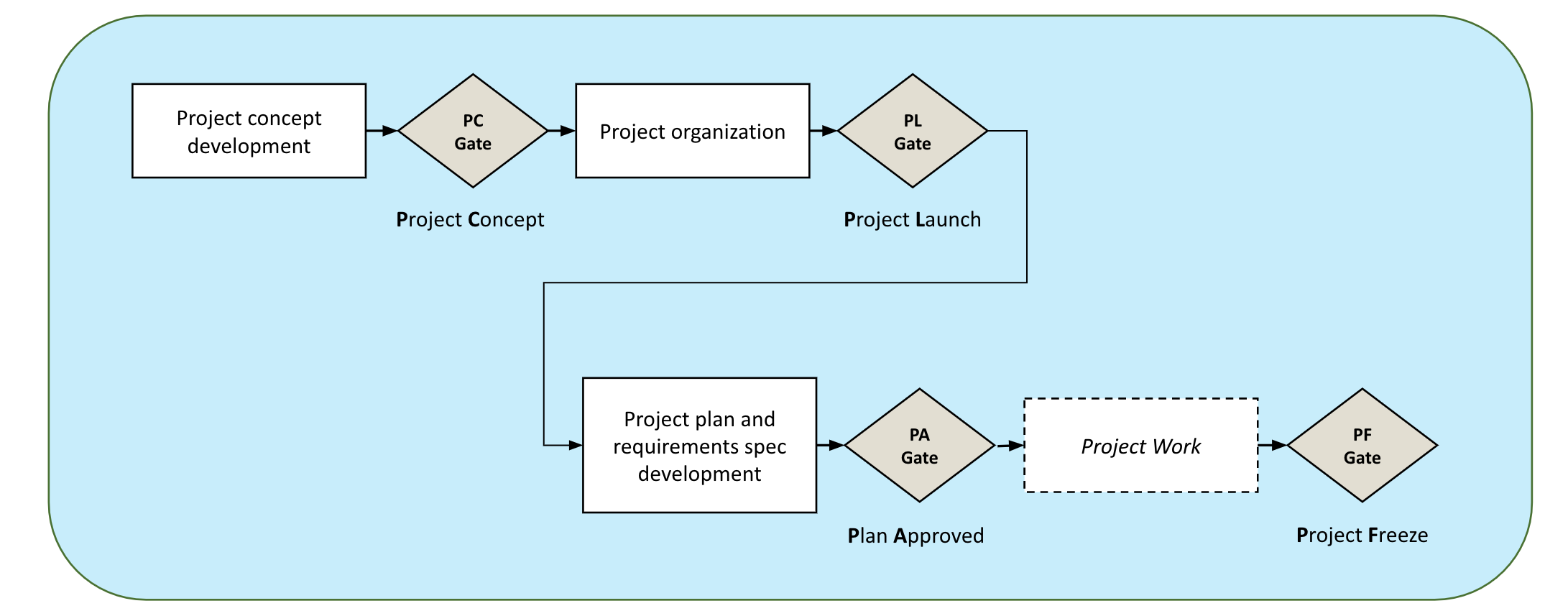

To select, plan, and coordinate OpenHW projects, the OpenHW Group uses a structured gate review process that defines checkpoints and checklists toward completion of industrial grade IP (Figure 2). These gates are tracked by project in the OpenHW Dashboard.

Figure 2: OpenHW Gate Review Process

We organize our working groups into a simple structure shown in Figure 3.

All OpenHW working groups are chaired by members and are open to participation from all OpenHW Group members. The Technical Working Group (TWG) has responsibility for technical process, roadmap, and project decisions. The Cores, Software, Hardware, and Verification Groups (TGs) organize technical project work and contribute to roadmap development within their respective focus area. The OpenHW Marketing Working Group disseminates our work through conferences, social media, publications and web-presence, including the OpenHW TV monthly webcast.

Finally, the OpenHW Asia Working Group (AWG) and OpenHW Europe Working Group (EWG) address regional open hardware requirements, technical project incubation, and data governance. With participation from key regional organizations and thought leaders they aim to foster a global, unified open hardware ecosystem while providing focus on specific Asian and European ecosystem considerations. Constituted as Eclipse Foundation Working Groups, AWG and EWG are open to participation from all joining members of OpenHW Group and Eclipse Foundation.

Figure 3: OpenHW Working Groups Structure

Industrial-Academic Collaboration Benefits All Parties

Collaboration between leading universities and industry under the OpenHW Group banner has proven extremely fruitful. We’re taking this even further with the OpenHW Accelerate Program. This program is co-sponsored by Mitacs and CMC. The program pairs companies that need researchers in the OpenHW fields, with researchers in Canadian and other universities and matches research funding dollar-for-dollar. The program’s first project is the CORE-V VEC (Vector Accelerator) project developed at Polytechnique Montréal in collaboration with ETH Zurich.

Stay Tuned and Get Involved

There’s plenty more to talk about that’s upcoming for the OpenHW Group, including:

- Multi-core CORE-V designs

- Chiplet interconnect

- Industry announcements supporting our MCU and DEVKIT projects

- Increased focus on AI and machine learning requirements for CORE-V

- Additional simulator support

- Industrialization of floating point units and accelerators

- Advances in core-v-verif

In the meantime, we encourage you to explore our projects, subscribe to our mailing lists, and contact info@openhwgroup.org for more information about getting involved!